I'm new to Verilog programming. I'm trying to work up to a 64-bit CLA by building a 4-bit CLA, then an 8-bit (out of 2 instances of a 4-bit), then a 16-bit (out of 2 instances of the 8-bit one). I'll provide my code, then an explanation of the problem I'm having.

I'm attempting to write a ripple carry adder in verilog. Module halfadder(a,b,sum,carry);input a,b;output sum,carry;assign sum=a^b;assign carry=a&b;endmodulemodule fulladder(a,b,cin,sum,cout);input a,b,cin;output sum,cout;wire t1,t2;halfadder h(a,b,t1,t2);assign cout=t1&cin;assign sum=t1^cin;assign cout=t2 cout;endmodule // fulladdermodule ripplecarryadder(input1,input2,answer);input 31:0 input1,input2;output 31:0 answer;integer carry,t;genvar i;initial beginassign carry=1'b0;endfor(i=0;i.assign statements are not to be used inside of statement blocks.

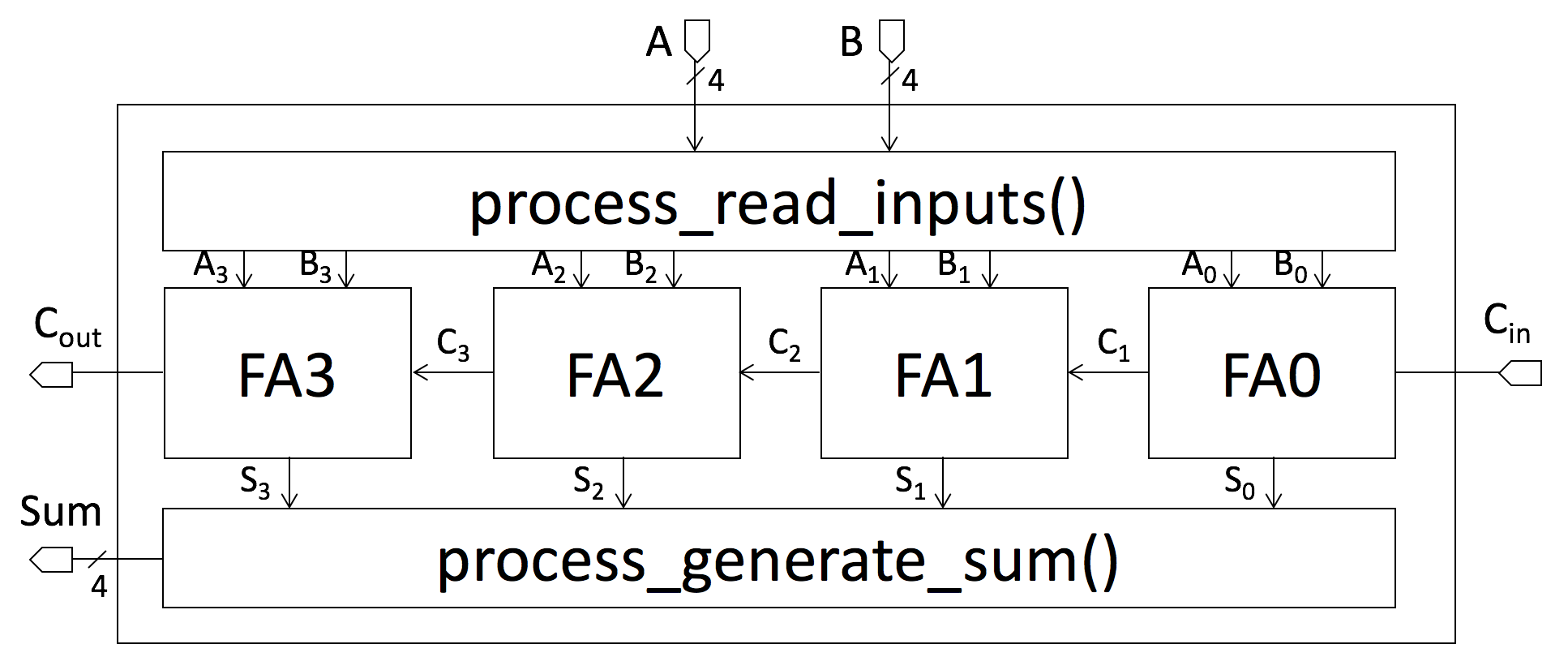

Extend the full bit adder so that it can add two 2 bit inputs in place of two 1 bit inputs. It will also have a carry in and a carry out.

Anytime you have a begin/ end block, the left-hand side of the statement gets set without using the assign keyword. E.g.: initial begincarry = 1'b0end.You cannot instantiate modules inside a procedural block or for-loop (e.g. Fulladder), you need to use a generate statement instead. You declared a genvar, so I think you meant to do this, but you don't seem to have the generate statement.You cannot drive a reg/integer type from the output of a module, reg/integers can only be driven from a procedural block. Change type t from an integer to a wire31:0 instead.

RSS Feed

RSS Feed